LDO电源电路应用中需要考虑电容的ESR。

LDO电源电路应用中需要考虑电容的ESR。在电路设计过程中,我们要考虑多的很多的问题,如电流大小,功率,电压,纹波等等因素。今天我们考虑的是LDO输出电路中,怎么选择电容ESR的大小。

选择电容大小决定了储存电荷及滤波的能力储存电荷,为负载电路提供瞬时电流支持,稳定输出电压。当负载电流瞬间增加时,输出电容能够快速提供额外的电荷,保证输出电压不会因此降低。LDO本身并不会产生噪声,除非其输入端或输出端受到外部谐波噪声干扰,所以LDO的输入输出电容是绝对必要的,而输出电容必须选择在安全的ESR范围里;

LDO输出滤波电容的选择关键是注意ESR范围,一般的LDO大都选用钽电容,因为它具有较好的ESR稳定范围,有利于LDO工作的稳定。

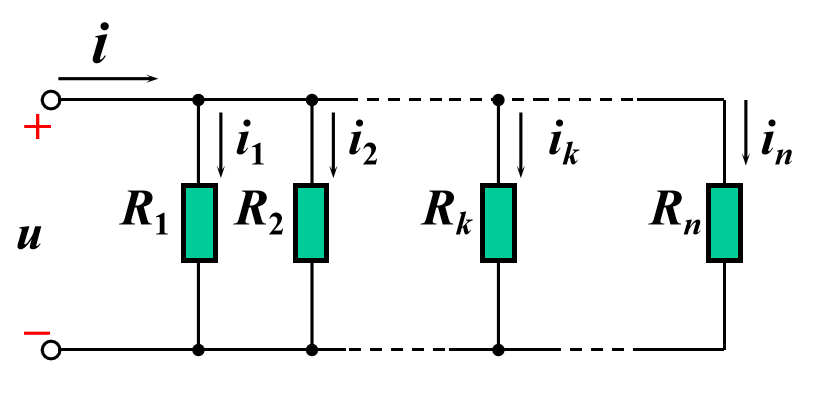

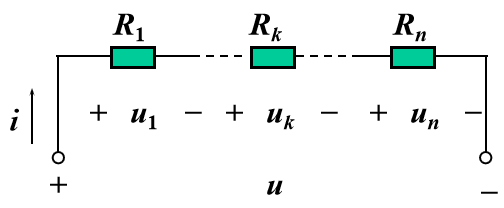

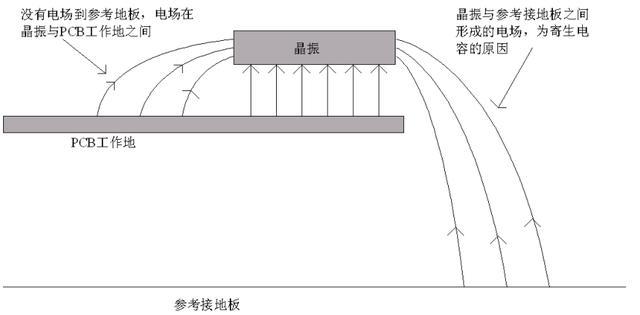

提到电容的 ESR,设计者往往想到的都是其负面影响。的确,较大的 ESR 有两个不利因素。第一,根据电容损耗角正切值的定义,较大的 ESR 会产生较大的损耗功率 P,如果P大到一定程度,且单板上该类型的电容器件数目较多时,功耗预算就不得不考虑电容上的损耗,这往往是电子设计工程师最不希望看到的。第二,对于高速电路设计,往往希望电容的阻抗越小越好。这有两个含义,一方面,对于高频信号的交流耦合,电容串联在高频信号上,目的是隔断高频信号收发两端的直流分量,同时又希望高频信号的衰减越小越好,如果电容的 ESR 较大,对于交流耦合的高频信号,相当于在信号中间串联了一个不小的电阻,将产生一定的衰减;,另一方面,对于并联在电源和地之间的滤波电容,其作用是为噪声等干扰信号提供一个极低阻抗的回路,ESR 较大的电容,显然无法起到这个作用。对于高速电路,即使 ESR 很小的电容,其 ESR 值仍不能满是低阻抗要求,因此,在重要的电源滤波电路上,往往需要并联多个电容,以最大程度地降低 ESR。

不过情况也有例外,LT1398电源芯片输出电路电容的 ESR 就被用于 LDO 芯片的高频补偿。其原理在于当LDO电源的负载电流发生瞬时变化时,利用 ESR 能立即产生电压波动,从而引起 LDO电源反馈电路的动作,以便 LDO 电源针对负载变化做出快速的调整

选择电容时,我们要理解以下三点:

1、电容器件并不是纯粹的电容,而是带有 ESR、ESL、Rleak 等分量的小型电路

2、ESL取决于电容器件的类型和封装,ESR 取决于工作温度、频率、导线电阻等

3大多数情况下,电容器件的 ESR 越小,电路性能越好,但也有例外,设计时需要根据器件的要求进行选型

最新发布