Altium Designer原理图总线设置要注意那些呢?

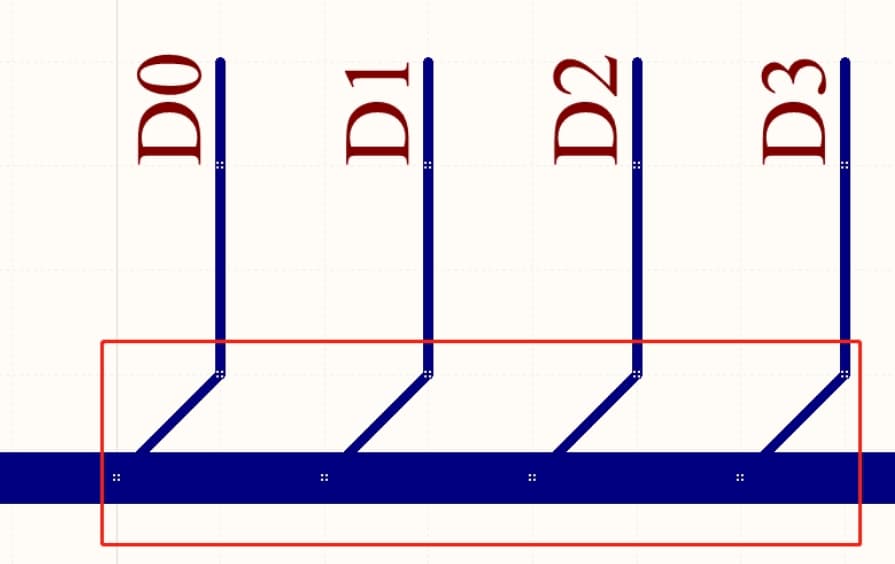

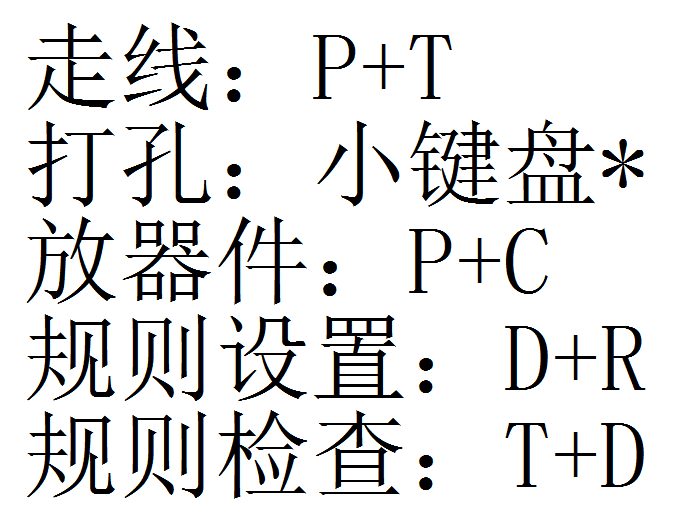

AD中,在设计时我们很多地方用到总线。这样有利用我们的观察。在放置总线快捷键(P+B),然后我们再画好导线(P+W),现放置总线分支(P+U)。在放置状态下,我们按TAB键,可以修改它们的属性。

在放置好的导线上,我们放置网络名称(P+N)。同一网络标签,其名称应该完全相同 (包括宇母大小写)。

一定要先画总线和延长线,然后在进行总线入口链接。如果先画总线入口在画总线,这种操作方法是错误的,你的总线链接有时会出现问题。链接顺序不同,链接的图形也有区别。注意红色框里的白点点。

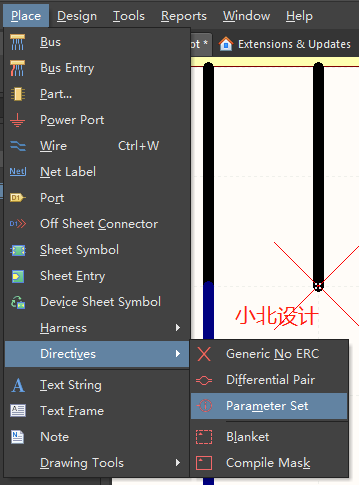

放置端口:按快速捷键“P+R”,按“Tab”键设置属性(名称、左右方向、输入/输出).

击确定端口的一个端口,再单击确定其另外一个端口,端口上面需要放一个和端口名称一样的标签。如上图的Data[0..3]。总线上一定要放在总线网络名。如果编译时出现Duplicate Net Names WireN000-1(Inferred)错误信息。那么你要把把端口名字修改下。

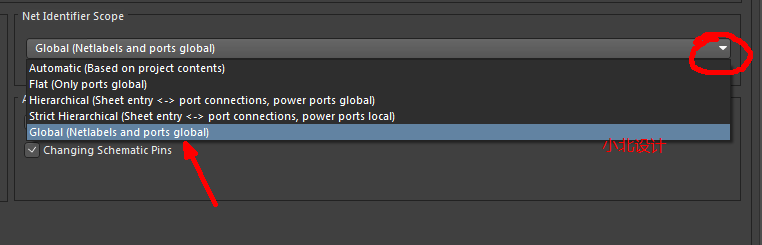

在原理图检查时,检查报告为:Duplicate Net Names Wire XXX

我们执行:打开Project(工程)》Project Option(工程参数)》Option卷标,在Net Identifier Scope(网络标识范围)一栏的四个选项(Automatic、Hierarchical、Flat、Global)中选择Global项,然后点确定就行了。

“Automatic”是缺省选项,表示系统会检测项目图纸内容,从而自动调整网络标识的范围。检测及自动调整的过程如下:如果原理图里有Sheet Entry标识,则网络标识的范围调整为Hierarchical。如果原理图里没有Sheet Entry标识。但是有Port标识,则网络标识的范围调整为Flat。如果原理图里既没有Sheet Entry标识,又没有Port标识,则Net Label的范围调整为Global。

“Flat”代表扁平式图纸结构,这种情况下,Net Label的作用范围仍是单张图纸以内。而Port的作用范围扩大到所有图纸,各图纸只要有相同的Port名,就可以发生信号传递。

“Hierarchical”代表层次式结构,这种情况下,Net Label,Port的作用范围是单张图纸以内。当然,Port可以与上层的Sheet Entry连接,以纵向方式在图纸之间传递信号。

“Global”是最开放的连接方式,这种情况下,Net Label、Port的作用范围都扩大到所有图纸。各图纸只要有相同的Port或相同的Net Label,就可以发生信号传递

最新发布