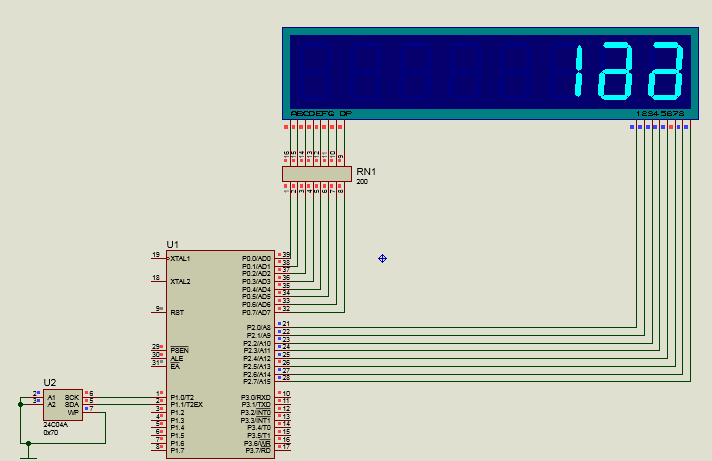

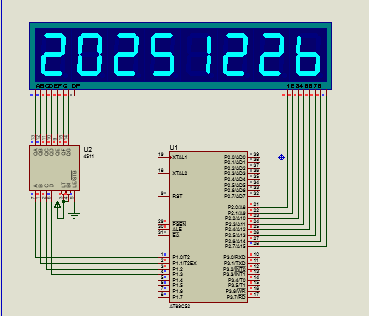

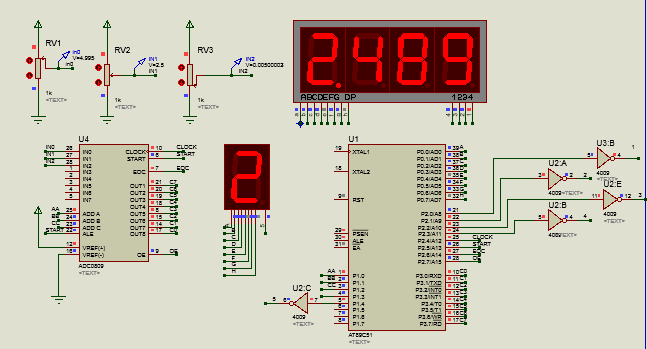

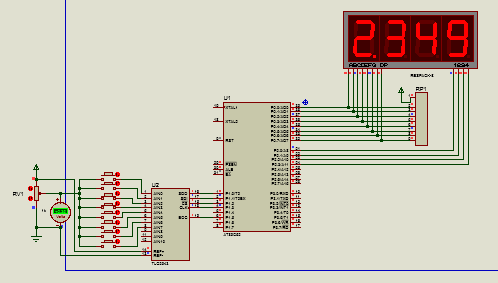

IC-24C04与数码管

//24c04支持双向两线总线和数据传输规程。若器件传送数据到总线上,

//则定义器件为发送器。若器件接收数据,则定义器件为接收器。总线必须在一个主器件控制工作,

//主器件产生串行时钟(SCl),控制总线存取,并且产生开始和停止条件。同时24c04a作为从器件工作。

//主器件和从器件都可工作于发送器的状态。但工作于何种方式由主器件决定。

/*引脚号 引脚名称

1 A0

2 A1

3 A2

功能说明:

地址输入。A2、A1和A0是器件地址输入引脚。

24C02/32/64使用A2、A1和A0输入引脚作为硬件地址,总线上可同时级联8个

24C02/32/64器件(详见器件寻址)。

24C04使用A2和A1输入引脚作为硬件地址,总线上可同时级联4个

24C04器件,A0为空脚,可接地。

24C08使用A2输入引脚作为硬件地址,总线上可同时级联2个24C08器

件,A0和A1为空脚,可接地。

24C16未使用器件地址引脚,总线上最多只可连接一个16K器件,A2、A1

和A0为空脚,可接地。

引脚号 引脚名称

5 SDA 串行地址和数据输入/输出。SDA是双向串行数据传输引脚,漏极开路,需外接上拉电阻到Vcc(典型值10kΩ)。

6 SCL 串行时钟输入。SCL同步数据传输,上升沿数据写入,下降沿数据读出。

//--------------

#include<reg51.h>

#include<intrins.h>

#define uchar unsigned char

#define uint unsigned int

#define delay4us(){_nop_();_nop_();_nop_();_nop_();}

sbit SCL= P1^0;

sbit SDA= P1^1;

//数码管段表,最后一字节为黑屏

uchar code shizi[]={0XC0,0XF9,0XA4,0XB0,0X99,0X92,0X82,0XF8,0X80,0X90,0XFF};

// 三位数的显示缓冲

uchar xianshi_wei[]={0,0,0};

uchar code xieru_shuzi[]={12,58,123};

uchar zongshu=0,jishu=0,jishu_2=0;

//延时

void yan_shi(uint ms)

{

uchar i,j;

for(i=0;i<ms;i++)

for(j=0;j<110;j++);

}

//IIC启动

void kaishi()

{

SDA=1;

SCL=1;

delay4us();

SDA=0;

delay4us();

SCL=0;

}

//IIC停止

void tingzhi()

{

SDA=0;

SCL=0;

delay4us();

SCL=1;

delay4us();

SDA=1;

}

//读取应答

void du_qu_danyi()

{

SDA=1;

delay4us();

SCL=1;

delay4us();

SCL=0;

}

//发送非应答信号

void fei_danyi()

{

SDA=1;

SCL=1;

delay4us();

SCL=0;

SDA=0;

}

//向24C04中写一字节

void xie_zijie(uchar zi)

{

uchar i;

for(i=0;i<8;i++)//循环移入8位

{

zi<<=1;

SDA=CY;

_nop_();

SCL=1;

delay4us();

SCL=0;

}

du_qu_danyi();

}

//向指定地址写数据

void zhiding_xieshuju(uchar add,uchar dat)

{

kaishi();

xie_zijie(0xa0);

xie_zijie(add);

xie_zijie(dat);

tingzhi();

yan_shi(10);

}

//从24C04中读一字节

uchar du_zijie()

{

uchar i,d;

for(i=0;i<8;i++)

{

SCL=1;

d<<=1;

d|=SDA;

SCL=0;

}

return d;

}

/*//任意地址写数据

void xie_shuju(uchar add,uchar dat)

{

kaishi();

xie_zijie(0xa0);

xie_zijie(add);

xie_zijie(dat);

tingzhi();

yan_shi(10);

}*/

//当前地址读数据

uchar duqu_dangqi_shuju()

{

uchar dat;

kaishi();

xie_zijie(0xa1);

dat=du_zijie();

fei_danyi();

tingzhi();

return dat;

}

//任意地址读取数据

uchar duqu_reyi_shiju(uchar addr)

{

kaishi();

xie_zijie(0xa0);

xie_zijie(addr);

tingzhi();

return duqu_dangqi_shuju();

}

//数据转换与显示

void shuju_xianshi()

{

xianshi_wei[2]=zongshu/100;

xianshi_wei[1]=zongshu%100/10;

xianshi_wei[0]=zongshu%100%10;

if(xianshi_wei[2]==0)

{

xianshi_wei[2]=10;

if(xianshi_wei[1]==0)

xianshi_wei[1]=10;

}

P2=0x80;

P0=shizi[xianshi_wei[0]];

yan_shi(2);

P2=0x40;

P0=shizi[xianshi_wei[1]];

yan_shi(2);

P2=0x20;

P0=shizi[xianshi_wei[2]];

yan_shi(2);

}

//主程序

void main()

{

uchar i;

IE=0x82;

TMOD=0X01;

TH0=(65536-5000)/256;

TL0=(65536-5000)%256;//定时50MS

TR0=1;

zongshu=duqu_reyi_shiju(0x00)+1;

zhiding_xieshuju(0x00,zongshu);

for(i=0;i<3;i++)

zhiding_xieshuju(i,xieru_shuzi[i]);

while(1)

{

shuju_xianshi();

zongshu=duqu_reyi_shiju(jishu_2);

}

}

//定时器0中断例程

void dingshiqi_1() interrupt 1

{

TH0=(65536-5000)/256;

TL0=(65536-5000)%256;//定时2MS

jishu++;

if(jishu==200)

{

jishu=0;

jishu_2++;

if(jishu_2==3)

jishu_2=0;

}

//则定义器件为发送器。若器件接收数据,则定义器件为接收器。总线必须在一个主器件控制工作,

//主器件产生串行时钟(SCl),控制总线存取,并且产生开始和停止条件。同时24c04a作为从器件工作。

//主器件和从器件都可工作于发送器的状态。但工作于何种方式由主器件决定。

/*引脚号 引脚名称

1 A0

2 A1

3 A2

功能说明:

地址输入。A2、A1和A0是器件地址输入引脚。

24C02/32/64使用A2、A1和A0输入引脚作为硬件地址,总线上可同时级联8个

24C02/32/64器件(详见器件寻址)。

24C04使用A2和A1输入引脚作为硬件地址,总线上可同时级联4个

24C04器件,A0为空脚,可接地。

24C08使用A2输入引脚作为硬件地址,总线上可同时级联2个24C08器

件,A0和A1为空脚,可接地。

24C16未使用器件地址引脚,总线上最多只可连接一个16K器件,A2、A1

和A0为空脚,可接地。

引脚号 引脚名称

5 SDA 串行地址和数据输入/输出。SDA是双向串行数据传输引脚,漏极开路,需外接上拉电阻到Vcc(典型值10kΩ)。

6 SCL 串行时钟输入。SCL同步数据传输,上升沿数据写入,下降沿数据读出。

7 WP 写保护。WP引脚提供硬件数据保护。当WP接地时,允许数据正常读写操作;当WP接Vcc时,写保护,只读。

通过网盘分享的文件:IIC—24c02

链接: https://pan.baidu.com/s/14NdZSaSthDpYjDsTJN_D-w 提取码: tjit

//--------------

#include<reg51.h>

#include<intrins.h>

#define uchar unsigned char

#define uint unsigned int

#define delay4us(){_nop_();_nop_();_nop_();_nop_();}

sbit SCL= P1^0;

sbit SDA= P1^1;

//数码管段表,最后一字节为黑屏

uchar code shizi[]={0XC0,0XF9,0XA4,0XB0,0X99,0X92,0X82,0XF8,0X80,0X90,0XFF};

// 三位数的显示缓冲

uchar xianshi_wei[]={0,0,0};

uchar code xieru_shuzi[]={12,58,123};

uchar zongshu=0,jishu=0,jishu_2=0;

//延时

void yan_shi(uint ms)

{

uchar i,j;

for(i=0;i<ms;i++)

for(j=0;j<110;j++);

}

//IIC启动

void kaishi()

{

SDA=1;

SCL=1;

delay4us();

SDA=0;

delay4us();

SCL=0;

}

//IIC停止

void tingzhi()

{

SDA=0;

SCL=0;

delay4us();

SCL=1;

delay4us();

SDA=1;

}

//读取应答

void du_qu_danyi()

{

SDA=1;

delay4us();

SCL=1;

delay4us();

SCL=0;

}

//发送非应答信号

void fei_danyi()

{

SDA=1;

SCL=1;

delay4us();

SCL=0;

SDA=0;

}

//向24C04中写一字节

void xie_zijie(uchar zi)

{

uchar i;

for(i=0;i<8;i++)//循环移入8位

{

zi<<=1;

SDA=CY;

_nop_();

SCL=1;

delay4us();

SCL=0;

}

du_qu_danyi();

}

//向指定地址写数据

void zhiding_xieshuju(uchar add,uchar dat)

{

kaishi();

xie_zijie(0xa0);

xie_zijie(add);

xie_zijie(dat);

tingzhi();

yan_shi(10);

}

//从24C04中读一字节

uchar du_zijie()

{

uchar i,d;

for(i=0;i<8;i++)

{

SCL=1;

d<<=1;

d|=SDA;

SCL=0;

}

return d;

}

/*//任意地址写数据

void xie_shuju(uchar add,uchar dat)

{

kaishi();

xie_zijie(0xa0);

xie_zijie(add);

xie_zijie(dat);

tingzhi();

yan_shi(10);

}*/

//当前地址读数据

uchar duqu_dangqi_shuju()

{

uchar dat;

kaishi();

xie_zijie(0xa1);

dat=du_zijie();

fei_danyi();

tingzhi();

return dat;

}

//任意地址读取数据

uchar duqu_reyi_shiju(uchar addr)

{

kaishi();

xie_zijie(0xa0);

xie_zijie(addr);

tingzhi();

return duqu_dangqi_shuju();

}

//数据转换与显示

void shuju_xianshi()

{

xianshi_wei[2]=zongshu/100;

xianshi_wei[1]=zongshu%100/10;

xianshi_wei[0]=zongshu%100%10;

if(xianshi_wei[2]==0)

{

xianshi_wei[2]=10;

if(xianshi_wei[1]==0)

xianshi_wei[1]=10;

}

P2=0x80;

P0=shizi[xianshi_wei[0]];

yan_shi(2);

P2=0x40;

P0=shizi[xianshi_wei[1]];

yan_shi(2);

P2=0x20;

P0=shizi[xianshi_wei[2]];

yan_shi(2);

}

//主程序

void main()

{

uchar i;

IE=0x82;

TMOD=0X01;

TH0=(65536-5000)/256;

TL0=(65536-5000)%256;//定时50MS

TR0=1;

zongshu=duqu_reyi_shiju(0x00)+1;

zhiding_xieshuju(0x00,zongshu);

for(i=0;i<3;i++)

zhiding_xieshuju(i,xieru_shuzi[i]);

while(1)

{

shuju_xianshi();

zongshu=duqu_reyi_shiju(jishu_2);

}

}

//定时器0中断例程

void dingshiqi_1() interrupt 1

{

TH0=(65536-5000)/256;

TL0=(65536-5000)%256;//定时2MS

jishu++;

if(jishu==200)

{

jishu=0;

jishu_2++;

if(jishu_2==3)

jishu_2=0;

}

}

最新发布