详细讲解Allegro等长设置的二种方法

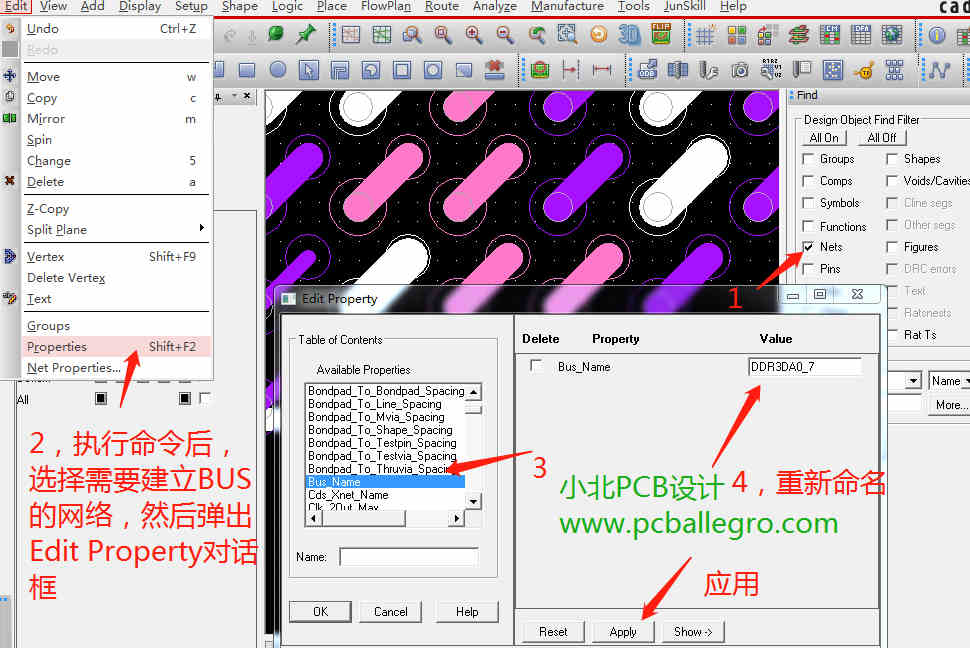

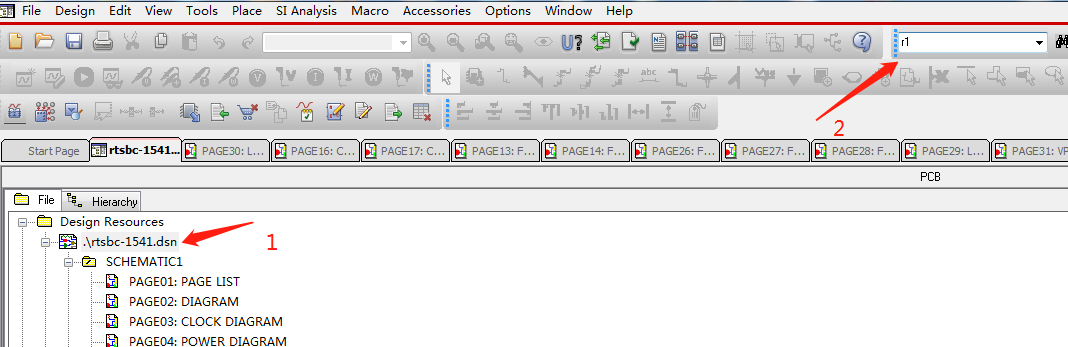

在建立等长时,我们都习惯都把同一类信号建立BUS,那在Cadence Allegro 16.6中,那如何建立BUS呢?小北PCB为详细讲解下:只选择网络后,执行Edit>Properties命令后,然后选择需要建立BUS的网络线。

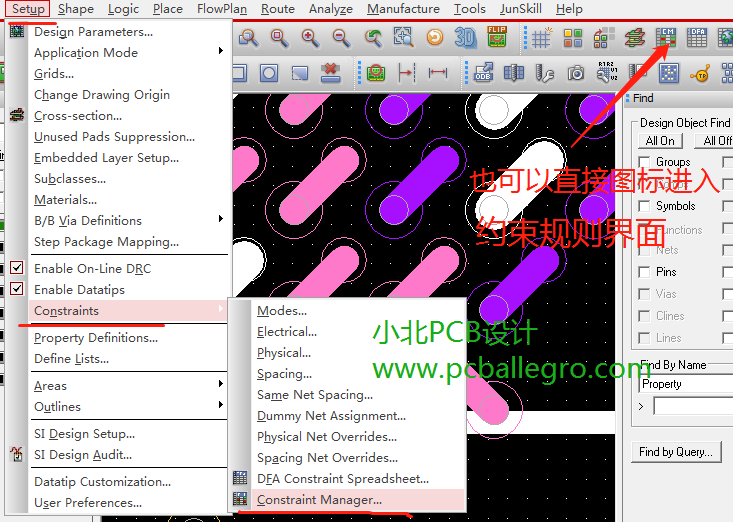

建立后,我们回到约束规则界面

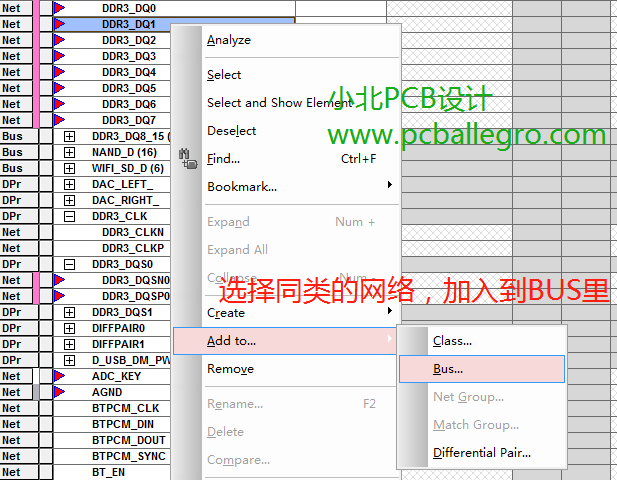

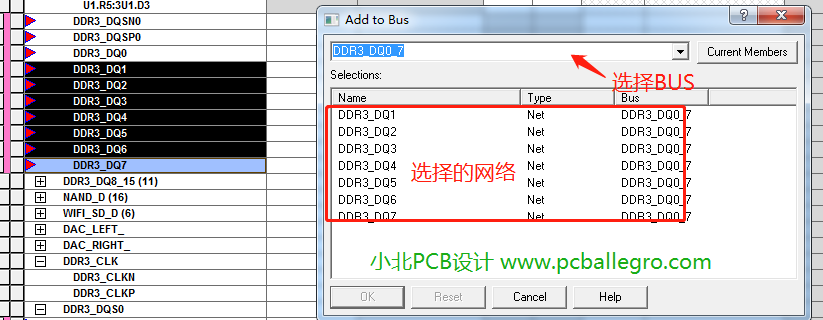

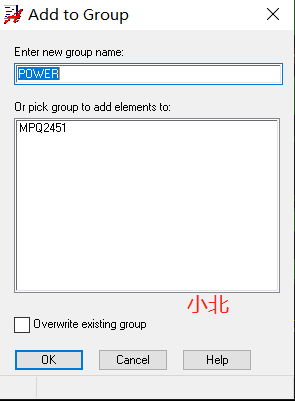

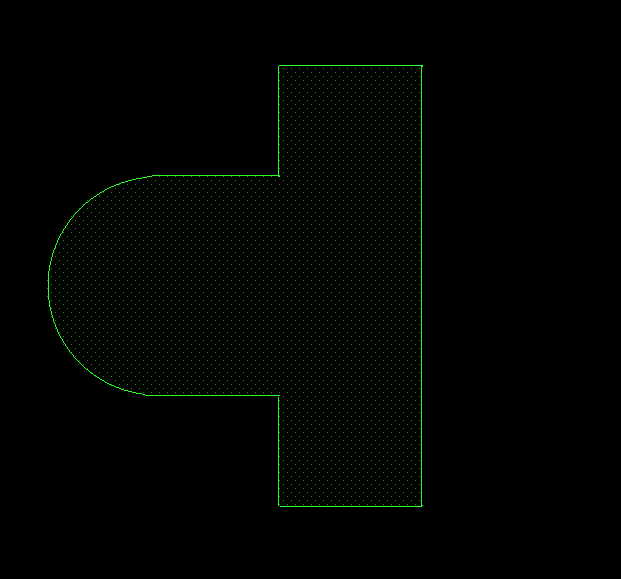

进入后,把同一类信号网络加入同一个BUS里,详细步骤如下图所示。

建立好BUS后,下面小北PCB详细介绍二种设置的方法。

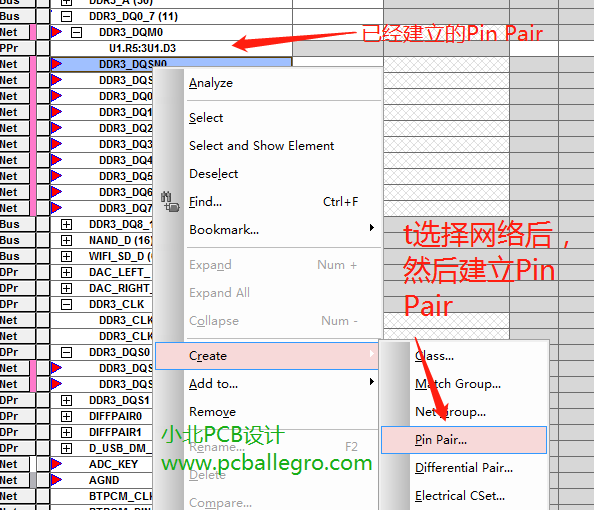

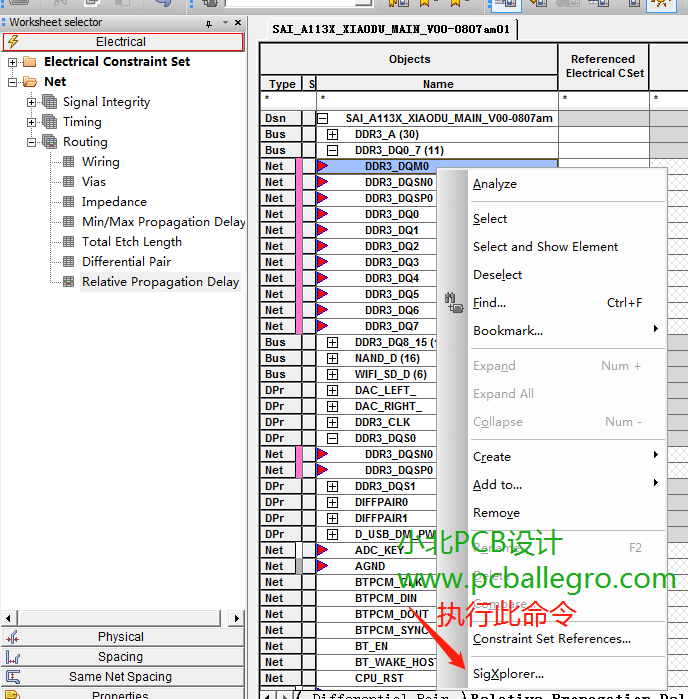

第一种:建立Pin Parir的方式来进行等长设置

然后弹出下面对话框,选择网络的两端。

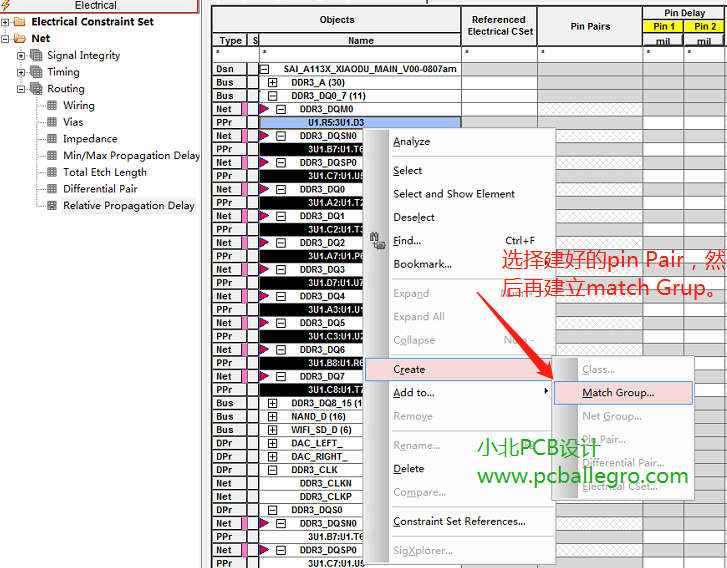

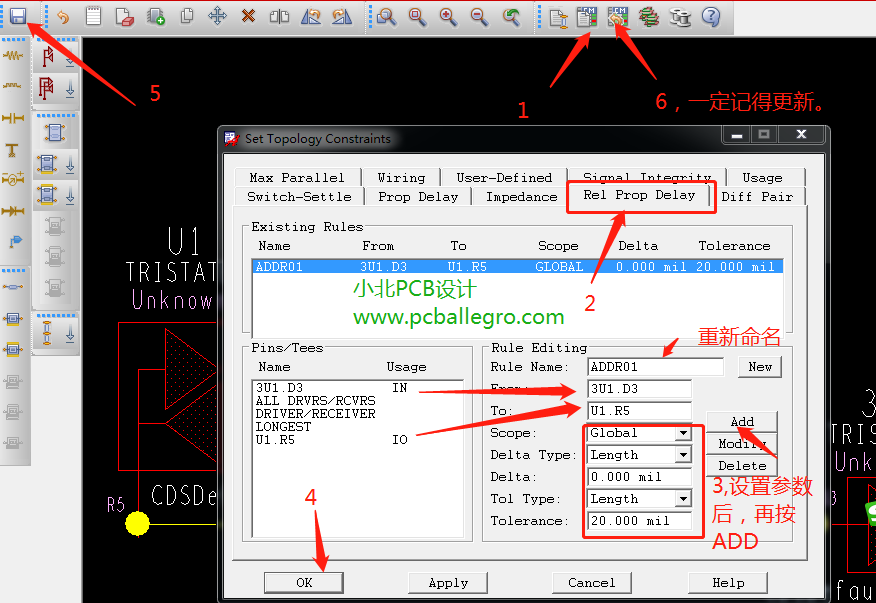

选择建立好的的Pin Pair再建立Match Group。

重新命名Match Group。

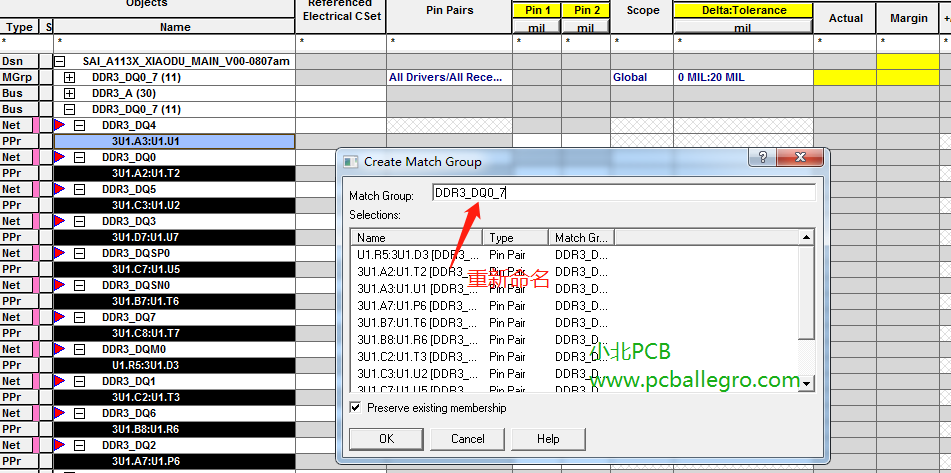

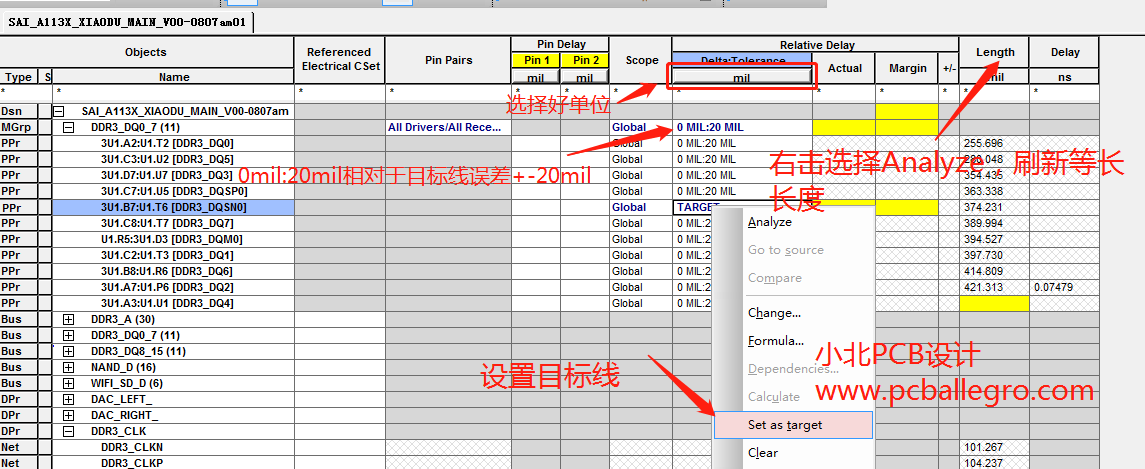

设置目标线,0mil:20mil是相对于目标线误差正负20mil。第一种设置的方法到这里结束,下面讲第二种:

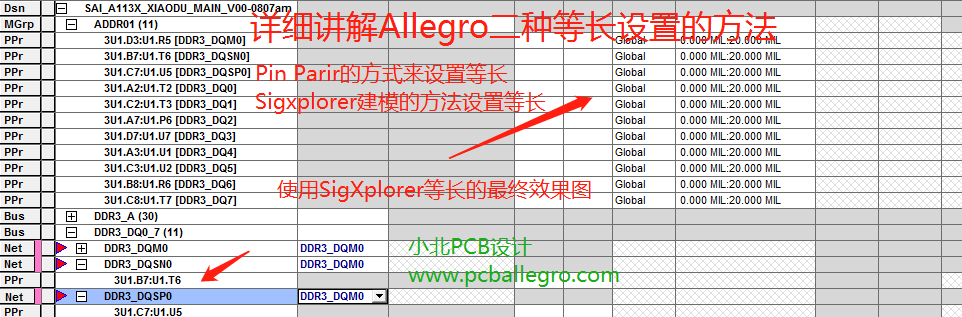

第二种:建立Sigxplorer模形的方法来设置等长,在建立模形之前,不要建立Xnet网络。

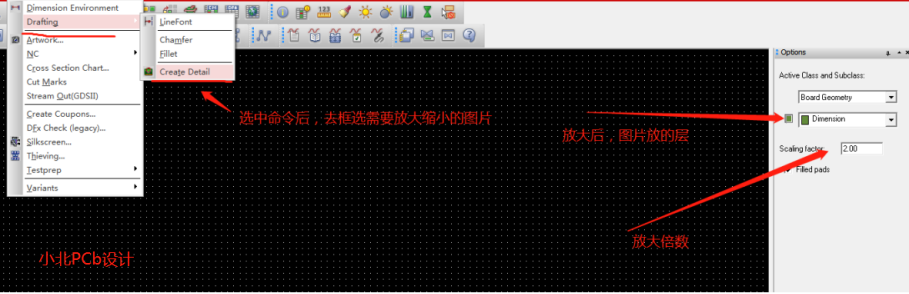

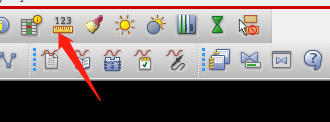

这个也需要建立BUS,这里就不多讲了,不懂的可以看下上面步骤,打开约束规则界面,执行Sigxplorer。

弹出下面对话框,根据图片进行设置,设置完成后,一定要记得更新,也就是下面的第6步。

模形完成后,效果如图所示:

原创由小北PCB发部,更多allegro等长设置尽在小北PCB,转载时请:请注明来自小北PCB,http://www.pcballegro.com/allegro/130.html。

最新发布